XC6SLX75-2FGG484C դաշտային ծրագրավորվող դարպասների զանգված

♠ Ապրանքի նկարագրություն

| Արտադրանքի հատկանիշ | Ատրիբուտի արժեք |

| Արտադրող՝ | Քսիլինքս |

| Ապրանքի կատեգորիա՝ | FPGA - Դաշտային ծրագրավորվող դարպասների զանգված |

| RoHS: | Մանրամասներ |

| Սերիա՝ | XC6SLX75 |

| Լոգիկայի տարրերի քանակը՝ | 74637 ԼԵ |

| Մուտքերի/ելքերի քանակը՝ | 280 մուտք/ելք |

| Մատակարարման լարում - Նվազագույն՝ | 1.14 Վ |

| Մատակարարման լարում - Առավելագույնը՝ | 1.26 Վ |

| Նվազագույն աշխատանքային ջերմաստիճանը՝ | 0°C |

| Առավելագույն աշխատանքային ջերմաստիճանը՝ | + 85°C |

| Տվյալների արագություն՝ | - |

| Հաղորդահաղորդիչների քանակը՝ | - |

| Մոնտաժման ոճը՝ | SMD/SMT |

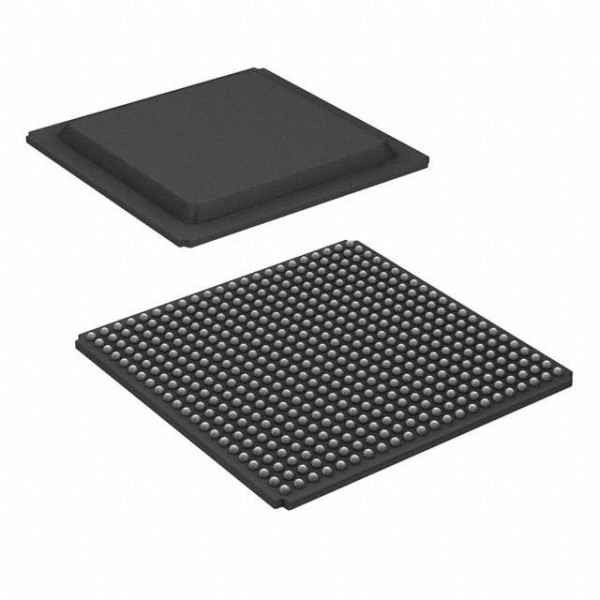

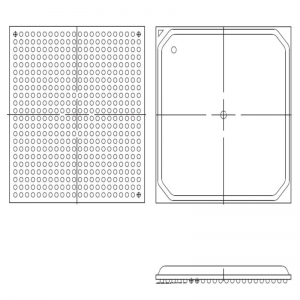

| Փաթեթ / Պատյան: | FCBGA-484 |

| Բրենդ՝ | Քսիլինքս |

| Բաշխված RAM: | 692 կբիթ |

| Ներկառուցված բլոկային օպերատիվ հիշողություն - EBR: | 3096 կբիթ |

| Առավելագույն աշխատանքային հաճախականությունը՝ | 1080 ՄՀց |

| Խոնավության նկատմամբ զգայուն՝ | Այո |

| Լոգիկական զանգվածի բլոկների քանակը - LAB-ներ՝ | 5831 ԼԱԲ |

| Աշխատանքային մատակարարման լարումը՝ | 1.2 Վ |

| Արտադրանքի տեսակը՝ | FPGA - Դաշտային ծրագրավորվող դարպասների զանգված |

| Գործարանային փաթեթի քանակը՝ | 1 |

| Ենթակատեգորիա՝ | Ծրագրավորվող տրամաբանական ինտեգրալ սխեմաներ |

| Առևտրային անվանում: | Սպարտացի |

| Միավորի քաշը։ | 1.662748 ունցիա |

♠ Սպարտան-6 ընտանիքի ակնարկ

Spartan®-6 ընտանիքը ապահովում է առաջատար համակարգային ինտեգրման հնարավորություններ՝ մեծ ծավալի կիրառությունների համար ամենացածր ընդհանուր արժեքով: Տասներեք անդամից բաղկացած ընտանիքը ապահովում է ընդլայնված խտություններ՝ 3,840-ից մինչև 147,443 տրամաբանական բջիջներով, նախորդ Spartan ընտանիքների էներգիայի սպառման կեսով, և ավելի արագ, ավելի համապարփակ կապակցվածությամբ: Կառուցված լինելով հասուն 45 նմ ցածր հզորության պղնձե պրոցեսորային տեխնոլոգիայի վրա, որն ապահովում է արժեքի, հզորության և արտադրողականության օպտիմալ հավասարակշռություն, Spartan-6 ընտանիքն առաջարկում է նոր, ավելի արդյունավետ, կրկնակի գրանցամատյանով 6 մուտքային որոնման աղյուսակի (LUT) տրամաբանություն և ներկառուցված համակարգային մակարդակի բլոկների հարուստ ընտրանի: Դրանք ներառում են 18 Կբ (2 x 9 Կբ) բլոկային RAM, երկրորդ սերնդի DSP48A1 շերտեր, SDRAM հիշողության կարգավորիչներ, բարելավված խառը ռեժիմի ժամացույցի կառավարման բլոկներ, SelectIO™ տեխնոլոգիա, հզորության օպտիմալացված բարձր արագությամբ սերիական ընդունիչ-հաղորդիչ բլոկներ, PCI Express® համատեղելի վերջնակետային բլոկներ, առաջադեմ համակարգային մակարդակի էներգիայի կառավարման ռեժիմներ, ավտոմատ հայտնաբերման կարգավորման տարբերակներ և բարելավված IP անվտանգություն՝ AES և սարքի DNA պաշտպանությամբ:

Այս առանձնահատկությունները ապահովում են մատչելի ծրագրավորվող այլընտրանք ASIC պատվերով պատրաստված արտադրանքներին՝ աննախադեպ օգտագործման հեշտությամբ: Spartan-6 FPGA-ները լավագույն լուծումն են մեծ ծավալի տրամաբանական նախագծման, սպառողական կողմնորոշմամբ DSP նախագծման և ծախսային զգայուն ներդրված կիրառությունների համար: Spartan-6 FPGA-ները ծրագրավորվող սիլիկոնային հիմք են Targeted Design Platforms-ի համար, որոնք ապահովում են ինտեգրված ծրագրային և ապարատային բաղադրիչներ, որոնք թույլ են տալիս նախագծողներին կենտրոնանալ նորարարության վրա՝ հենց որ սկսվի իրենց մշակման ցիկլը:

• Սպարտան-6 ընտանիք։

- Spartan-6 LX FPGA. Լոգիկայի համար օպտիմալացված

- Spartan-6 LXT FPGA: Բարձր արագությամբ սերիական միացում

• Նախագծված է ցածր գնի համար

- Բազմաթիվ արդյունավետ ինտեգրված բլոկներ

- Մուտքի/ելքի ստանդարտների օպտիմալացված ընտրություն

- Աստիճանավոր բարձիկներ

- Մեծ ծավալի պլաստիկ մետաղալարով միացված փաթեթներ

• Ցածր ստատիկ և դինամիկ հզորություն

- 45 նմ պրոցես՝ օպտիմալացված արժեքի և ցածր էներգիայի համար

- Զրոյական էներգիայի դեպքում ձմեռային անջատման ռեժիմ

- Կասեցման ռեժիմը պահպանում է վիճակը և կոնֆիգուրացիան բազմակի միացման արթնացման, կառավարման բարելավման միջոցով

- Ցածր հզորության 1.0V միջուկի լարում (միայն LX FPGA-ներ, -1L)

- Բարձր արդյունավետությամբ 1.2V միջուկի լարում (LX և LXT FPGA-ներ, -2, -3 և -3N արագության աստիճաններ)

• Բազմավոլտ, բազմաստանդարտ SelectIO™ ինտերֆեյսային բանկեր

- Մինչև 1080 Մբ/վ տվյալների փոխանցման արագություն մեկ դիֆերենցիալ մուտքի/ելքի համար

- Ընտրովի ելքային սկավառակ, մինչև 24 մԱ մեկ կապոցի համար

- 3.3V-ից մինչև 1.2VI/O ստանդարտներ և արձանագրություններ

- Ցածրարժեք HSTL և SSTL հիշողության ինտերֆեյսներ

- Տաք փոխարինման համապատասխանություն

- Կարգավորելի մուտքի/ելքի արագություն՝ ազդանշանի ամբողջականությունը բարելավելու համար

• Բարձր արագությամբ GTP սերիական փոխանցող-հաղորդիչներ LXT FPGA-ներում

- Մինչև 3.2 Գբ/վ

- Բարձր արագության ինտերֆեյսներ, ներառյալ՝ Serial ATA, Aurora, 1G Ethernet, PCI Express, OBSAI, CPRI, EPON, GPON, DisplayPort և XAUI

• PCI Express նախագծերի համար ինտեգրված վերջնակետային բլոկ (LXT)

• 33 ՄՀց, 32 և 64-բիթային սպեցիֆիկացիայի հետ համատեղելի ցածրարժեք PCI® տեխնոլոգիայի աջակցություն։

• Արդյունավետ DSP48A1 կտորներ

- Բարձր արդյունավետությամբ թվաբանություն և ազդանշանի մշակում

- Արագ 18 x 18 բազմապատկիչ և 48-բիթանոց կուտակիչ

- Խողովակաշարերի և կասկադային հնարավորություններ

- Նախնական ավելացում՝ ֆիլտրի ծրագրերին օգնելու համար

• Ինտեգրված հիշողության կառավարիչի բլոկներ

- DDR, DDR2, DDR3 և LPDDR աջակցություն

- Տվյալների փոխանցման արագությունը մինչև 800 Մբ/վ (12.8 Գբ/վ գագաթնակետային թողունակություն)

- Բազմամուտքային ավտոբուսային կառուցվածք՝ անկախ FIFO-ով, որը նվազեցնում է նախագծման ժամանակային խնդիրները

• Առատ տրամաբանական ռեսուրսներ՝ ավելացված տրամաբանական հզորությամբ

- Լրացուցիչ shift ռեգիստրի կամ բաշխված RAM-ի աջակցություն

- Արդյունավետ 6 մուտքային LUT-ները բարելավում են կատարողականությունը և նվազագույնի հասցնում հզորությունը

- LUT՝ կրկնակի ֆլիպ-ֆլոպերով, խողովակաշարային կենտրոնացված կիրառությունների համար

• Բլոկային RAM՝ լայնածավալ հատիկավորմամբ

- Արագ բլոկային RAM՝ բայթերի գրման հնարավորությամբ

- 18 Կբ բլոկներ, որոնք կարող են ըստ ցանկության ծրագրավորվել որպես երկու անկախ 9 Կբ բլոկային օպերատիվ հիշողություններ

• Ժամացույցի կառավարման սալիկ (CMT)՝ բարելավված կատարողականության համար

- Ցածր աղմուկ, ճկուն ժամացույցի կարգավորում

- Թվային ժամացույցի կառավարիչները (DCM) վերացնում են ժամացույցի թեքությունը և աշխատանքային ցիկլի աղավաղումը

- Փուլային կողպված օղակներ (PLL) ցածր թրթռման ժամանակաչափման համար

- Հաճախականության սինթեզ՝ միաժամանակյա բազմապատկմամբ, բաժանմամբ և փուլային տեղաշարժով

- Տասնվեց ցածր թեքության գլոբալ ժամացույցային ցանցեր

• Պարզեցված կոնֆիգուրացիա, աջակցում է ցածրարժեք ստանդարտներին

- 2-փինային ավտոմատ հայտնաբերման կարգավորում

- Լայնածավալ երրորդ կողմի SPI (մինչև x4) և NOR flash աջակցություն

- Հագեցած գործառույթներով Xilinx Platform Flash՝ JTAG-ով

- MultiBoot աջակցություն հեռակա թարմացման համար բազմաթիվ բիթհոսքերով, օգտագործելով watchdog պաշտպանությունը

• Դիզայնի պաշտպանության համար բարելավված անվտանգություն

- Դիզայնի նույնականացման համար սարքի ԴՆԹ-ի եզակի նույնականացուցիչ

- AES բիթային հոսքի կոդավորումը ավելի մեծ սարքերում

• Ավելի արագ ներդրված մշակում՝ բարելավված, ցածր գնով MicroBlaze™ փափուկ պրոցեսորով

• Արդյունաբերության առաջատար մտավոր սեփականության և հղման նախագծեր